Výkonné aplikace s hard real-time řízením mohou být díky svým požadavkům na zpoždění a jitter nesmírně náročné. Současný návrh pak zpravidla obsahuje kombinaci mikrokontroléru, RTOS (Real – Time Operating System) a aplikačního firmware coby podmínek pro náležitou výkonnost, spolehlivost a také úspěšnost nového embedded produktu. Velký důraz při podpoře hard real – time systémů přitom bývá kladen právě na RTOS, zatímco na samotnou architekturu mikrokontrolérů již nezbývá tolik prostoru. Navíc, pokud celé řešení v dobré víře vylepšíme rychlejším taktováním, musíme počítat s ještě větší výkonovou ztrátou nebo složitějším obvodovým řešením.

Innovasic Semiconductor se na to již nevydržel déle dívat a přistoupil k radikálnímu řešení, při kterém předefinoval hranice mezi úlohami křemíku a smyslem obslužného softwaru. Vznikla tak nová architektura, která vedle vyšší spolehlivosti a bezpečnosti navíc výrazně zjednodušuje vývoj i následné testování řídicích aplikací typu hard real – time.

Mikrokontrolér fido s logem pejska, zapouzdřený v 208pinovém PQFP

Architektura hard real – time mikrokontroléru

Innovasic pojmenoval novou rodinu mikrokontrolérů zkratkou fido, což jednoduše znamená flexible input, deterministic output. Filosofie návrhu vychází ze základní skutečnosti, že samotný křemík je relativně levný ve srovnání s nákladným vývojem embedded softwaru. Architektura fido změnila pohled na hranice mezi hardwarem a softwarem a přesunula funkce dosud běžně řízené programem přímo na čip. Tímto způsobem mohou vývojáři embedded systémů elegantněji zpracovat své představy včetně požadavků na zpoždění, jitter a vysokou spolehlivost real – time aplikací.

Innovasic pojmenoval novou rodinu mikrokontrolérů zkratkou fido, což jednoduše znamená flexible input, deterministic output. Filosofie návrhu vychází ze základní skutečnosti, že samotný křemík je relativně levný ve srovnání s nákladným vývojem embedded softwaru. Architektura fido změnila pohled na hranice mezi hardwarem a softwarem a přesunula funkce dosud běžně řízené programem přímo na čip. Tímto způsobem mohou vývojáři embedded systémů elegantněji zpracovat své představy včetně požadavků na zpoždění, jitter a vysokou spolehlivost real – time aplikací.

Třebaže je fido architektura zbrusu nová, byla navržena pro spolupráci s kódově kompatibilním instrukčním setem 68000. Osvědčená podoba CPU32+ se však neomezuje pouze na spolehlivé nástroje pro rodinu fido obvodů, ale byla navíc optimalizována pro real – time a další kritické aplikace, třeba z hlediska bezpečnosti. Prvním z mikrokontrolérů fido se stal obvod fido1100, nabízející deterministické zpracování, precizní context switching a předvídatelné zpoždění přerušení pro úlohy zpracovávané v reálném čase. Běh se přitom může odehrávat na hodinovém kmitočtu pouhých 66 MHz, což ve výsledku ještě ušetří nemalé výkonové ztráty.

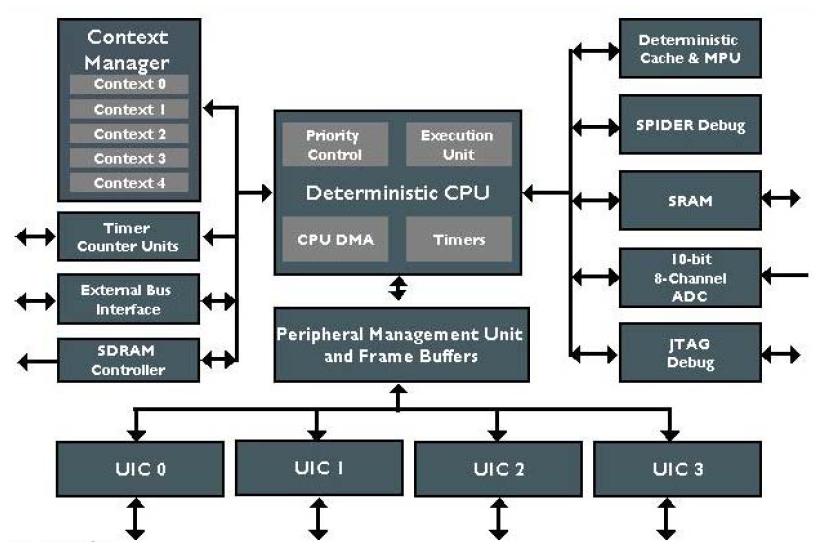

Real – time mikrokontrolér fido1100 vychází z 32bitové architektury

fido1100 obsahuje context manager pro pět nezávislých hardwarových kontextů. Nalezneme zde dva 32bitové timer control unity, watchdog a context timer. Externí sběrnicové rozhraní je 8, 16 nebo 32bitové a nabízí programovatelné chip selecty včetně memory controlleru. Na čipu dále najdeme deterministickou cache, Memory Protection Unit (MPU), SPIDER Debug interface, SDRAM Controller, vysokorychlostní SRAM 6k x 32, 10bitový A/D převodník v 8kanálovém provedení nebo třeba JTAG Debug interface pro emulaci a ladění. Vyhrazená jednotka Peripheral Management Unit (PMU) s integrovanými datovými frame buffery ovládá čtyři UIC (Universal I/O Controller), čímž vytváří pružné periferie s podporou celé řady požadavků na ně kladených. fido1100 pracuje s napájecím napětím 3.3 V a 5 V tolerantními I/O. 208pinové pouzdro PQFP nebo FBGA je stavěno pro průmyslový rozsah okolních teplot.

Komunikační protokoly

Jak již bylo řečeno, fido1100 obsahuje čtyři unikátní UIC (Universal I/O Controller) s podporou komunikačních protokolů nejrůznějších platforem. Pokud kontroléry pracují s integrovanou jednotkou Peripheral Management Unit (PMU) a datovými buffery, vyžaduje rozhraní ke své činnosti minimální účast procesorového jádra. Tato vlastnost následně procesoru umožňuje zužitkovat své prostředky na mnohem důležitější operace než je „pouhé“ řízení toku dat.

Každá jednotka UIC podporuje následující protokoly:

- 10/100 Ethernet, half a full duplex

- Filtrace MAC adresy

- Až 72 Smart GPIO

- 16550 UART

- Volitelně 2kanálový, 16550 kompatibilní UART

- Velikost Rx a Tx bufferu může odpovídat přenosové rychlosti na rozhraní

- CAN 2.0B

- I2C

- Serial Peripheral Interface (SPI)

- Vlastní zákaznické protokoly

Fast Context Switching

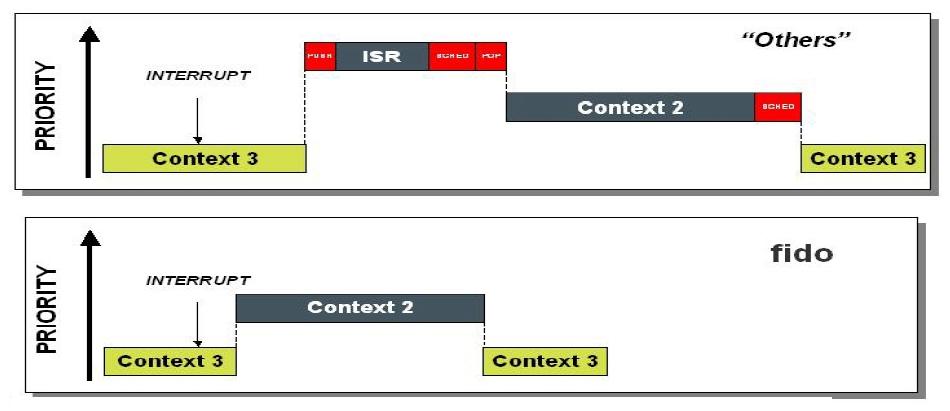

Typický mikrokontrolér nedělá žádné zásadní rozdíly mezi reálným časem, kritickou bezpečností, uživatelským rozhraním nebo aplikačním kódem uživatele, protože jednotlivé odlišnosti definuje až použitý software – RTOS. Problém však spočívá v tom, jak dalece může vývojář ovládat a dohlížet na úlohy běžící pod RTOS. Architektura fido naproti tomu řídí spoustu real – time úloh přímo z „křemíku“, což poskytuje výrazně lepší možnosti. Obrázek znázorňuje rozdíly mezi typickým mikrokontrolérem a řešením v podobě fido.

V obvodech fido1100 je spousta real – time úloh řízených hardwarově

fido se vyznačuje několika rysy, které byly záměrně vyvinuty pro snížení softwarové režie během řízení a přepínání jednotlivých úloh. Navržená architektura vymezuje priority v rámci jednoho z pěti oddělených hardwarových kontextů, které pracují jako „virtuální CPU“ Precizní řízení následně vytváří předvídatelné mechanismy pro zajištění tolik potřebné rychlé odezvy v rámci deterministické činnosti koncového zařízení.

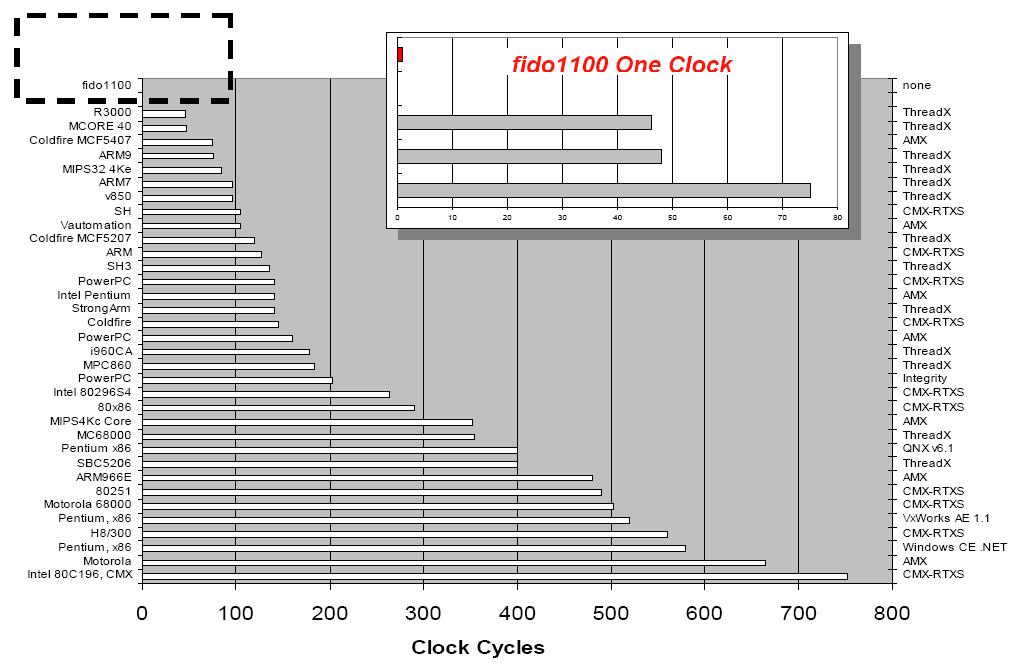

fido1100 může změnit kontext v jednom hodinovém cyklu

Prostorové a časové dělení uvnitř čipu zajišťuje náležitou posloupnost bez možnosti „vytuhnutí“. V praxi to pak znamená, že uživatelské rozhraní a kód s nízkou prioritou nebudou překážet real – time aktivitám nebo činnostem s nálepkou safety – critical. V případě přerušení se aktuální kontext jednoduše zastaví a přepne na nový. Po vykonání přerušení se opět aktivuje původní kontext v místě svého „vytržení“.

fido1100 nabízí optimalizované přepínání kontextu v rámci jednoho hodinového cyklu

Memory Protection Unit (MPU) řídí v souvislosti s pamětí a bez dalšího zásahu programu požadavky různých kontextů. Určité bloky paměti se pak ke svým specifickým kontextům přiřazují během bootování. Hardware se také umí vypořádat se situací, kdy nikdo nic nepotřebuje. Procesor pak okamžitě bez účasti kódu upadá do auto – sleep módu. Programátor se tak může věnovat jiným, důležitějším věcem. Při výskytu dalšího přerušení se pak mikroprocesor okamžitě probouzí zpátky k plnohodnotnému životu.

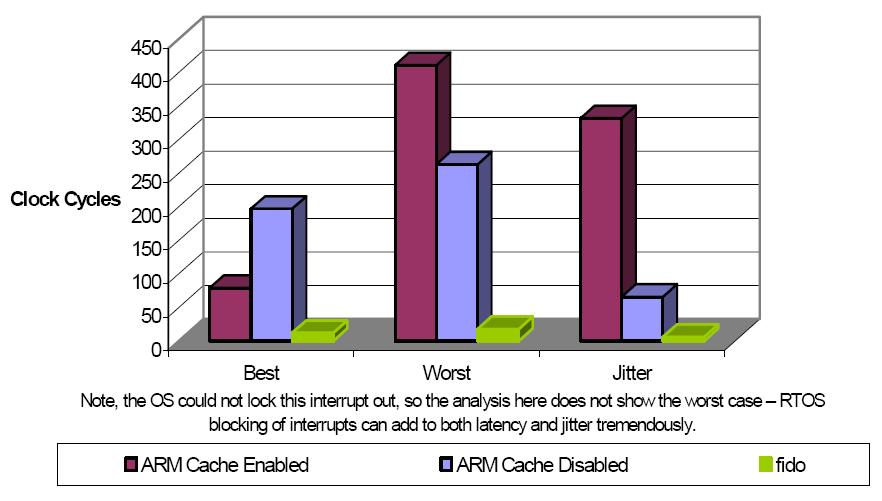

Uživatelsky programovatelná „deterministická cache“

Na rozdíl od PC systémů musí být real – time úlohy prováděny předvídatelným způsobem, v přesných časových intervalech a s minimální prodlevou, která bude navíc vykazovat zanedbatelné tolerance. Pokud se zpoždění stane nepředvídatelným, hovoříme o jitteru. U typických mikrokontrolérů se s jitterem dokážeme vypořádat tak, že zvedneme taktovací kmitočet, kterým následně snížíme zpoždění a konečně umravníme jitter do přijatelných mezí. Zároveň ale také vyprodukujeme větší množství ztrátového tepla, což může být nemalým problémem.

V rodině obvodů fido jitter snižujeme jinak, pomocí deterministické, kontextově uvědomělé cache s náležitou odezvou. Pod softwarovým dohledem, typicky během bootování, zde ukládáme a následně uchováváme k použití kritické části kódu.

Deterministická cache v obvodech fido1100

Problémy s laděním hard real – time systémů

Ladění (debugging, jindy také odvšivení) bývá u real – time systémů velmi náročné, protože jediná skrytá chyba může s přehledem způsobit nečekané problémy nebo dokonce nemožnost cokoli ovládat v reálném čase. Innovasic proto na vši, mouchy a podobnou firmwarovou havěť vypustil pavouka. Na rozdíl od běžně užívaných mikrokontrolérů a jejich softwarových nástrojů používá SPIDER křemíková hradla na čipu, kterými si generuje potřebná data, nastavuje body přerušení a sledovací body v rámci poctivého single – step debugu, čímž eliminuje potřebu instrumentace kódu, která by navíc přinesla další změny v chování a znesnadnila tak účinné odhalení problémů.

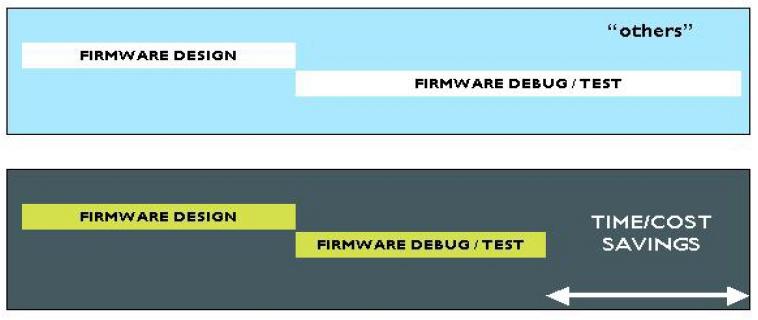

SPIDER účinně snižuje dobu potřebnou k ladění programu včetně dalších nákladů na testování

Trasy lze zapisovat do systémové paměti a následně využít služeb logického analyzátoru, zachytávajícího data a jejich časové údaje pro pozdější rozbory. Debugovací prostředí také umožňuje statistickou programovou analýzu, která vytipuje kritické části kódu, vhodné pro přesun do deterministické cache.

Vývojový kit pro obvody fido1100

Na závěr

Innovasic nabízí vývojářům novou architekturu mikrokontrolérů pro embedded aplikace s posunutými hranicemi mezi úlohami křemíku a tradičního RTOS / aplikačního firmwaru. Rychle tak můžeme využívat deterministický context switching, „deterministickou cache“ nebo díky on – chip context managementu potlačovat nežádoucí jitter. Čipy se již nebudou zahřívat neúměrně rychlým taktováním a ladění hard real – time systémů konečně přestane být díky vestavěným hradlům a jejich možnostem postrachem a noční můrou nejednoho vývojáře.

Download a odkazy:

- Domovská stránka Innovasic Semiconductor: http://www.innovasic.com/