Setkala jsem se již se zákazníky, kteří si stěžovali, že jim naše společnost odeslala špatný výrobek. Když jsem se pak zeptala na to, jakou poruchu součástka vykazuje, řekli mi: „Jen to nechce pracovat“. A tak zjišťuji, že si vývojáři mnohdy neuvědomují rizika, spojovaná s EOS (Electrical Overstress, v dalším textu budeme překládat jako elektrické přetížení), při kterých nechtěně vyrábí problémy tohoto druhu.

Setkala jsem se již se zákazníky, kteří si stěžovali, že jim naše společnost odeslala špatný výrobek. Když jsem se pak zeptala na to, jakou poruchu součástka vykazuje, řekli mi: „Jen to nechce pracovat“. A tak zjišťuji, že si vývojáři mnohdy neuvědomují rizika, spojovaná s EOS (Electrical Overstress, v dalším textu budeme překládat jako elektrické přetížení), při kterých nechtěně vyrábí problémy tohoto druhu.

Očividnou příčinou elektrického přetížení se například stává elektrostatický výboj (Electrostatic Discharge, ESD), ke kterému dochází tehdy, nachází – li se v těsné blízkosti dvě tělesa s odlišnými elektrostatickými potenciály, resp. rozdílem v řádu stovek až tisíců voltů. Pojďme však ještě dále. Další podmínka pro vznik EOS se může vyskytnout tehdy, dojde – li k aktivaci většího počtu napájecích zdrojů daného systému v různých časech. Na pinu nebo také více pinech konkrétního obvodu se tak možná vyskytne nežádoucí přepětí. Ještě jiným „spouštěčem“ přetížení se stane signál z „okolního světa“ či oddělené části systému pod odlišným napájením, který se pak vyskytne na vstupu nebo také výstupu zesilovače.

Chceme – li navrhovat spolehlivé a zároveň jednoduše vyrobitelné systémy s minimálním počtem skrytých provozních poruch, měli bychom v konkrétním zapojení věnovat pozornost potenciálu přepěťových stavů.

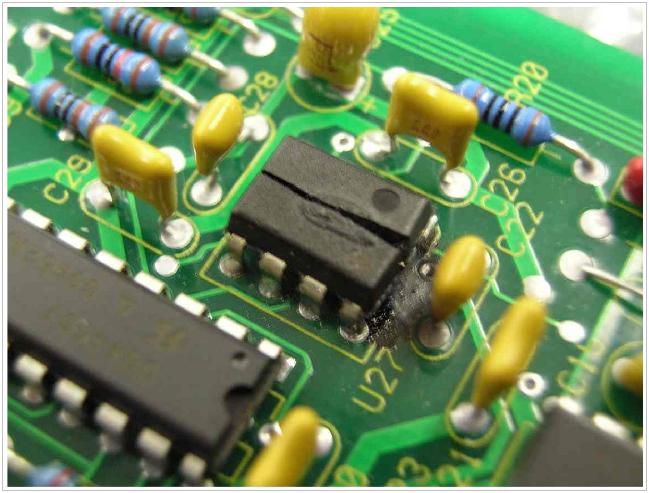

Možná se přitom budeme podvědomě spoléhat na vnitřní ESD struktury obvodu, zajišťující ochranu během elektrického přetížení. Třeba přitom zjistíme, že i dokonale provozuschopný integrovaný obvod ve fázi před připojením napájecího napětí se krátce po přivedení napájení a vstupních signálů znenadání poškodí. Elektrické přetížení přitom může být tak dramatické, že nadměrný ohřev roztaví čip včetně pouzdra a jejich materiálů, viz docela výmluvný obr. 1.

Obr. 1: Integrovaný obvod, poškozený v důsledku elektrického přetížení

Integrované obvody (IO) – zesilovače nemívají automaticky ochranu pro případ elektrického přetížení – EOS. V ideálním případě se pak interní ESD struktury během přetížení aktivují a zajišťují tak dostatečnou ochranu systému. Samotná skutečnost, že již máme na čipu ochranné prvky ESD, však ještě neznamená, že budeme chráněni před všemi problémy, spojovanými s přetížením.

Samotná skutečnost, že již máme na čipu ochranné prvky ESD, však ještě neznamená, že budeme chráněni před všemi problémy, spojovanými s přetížením.

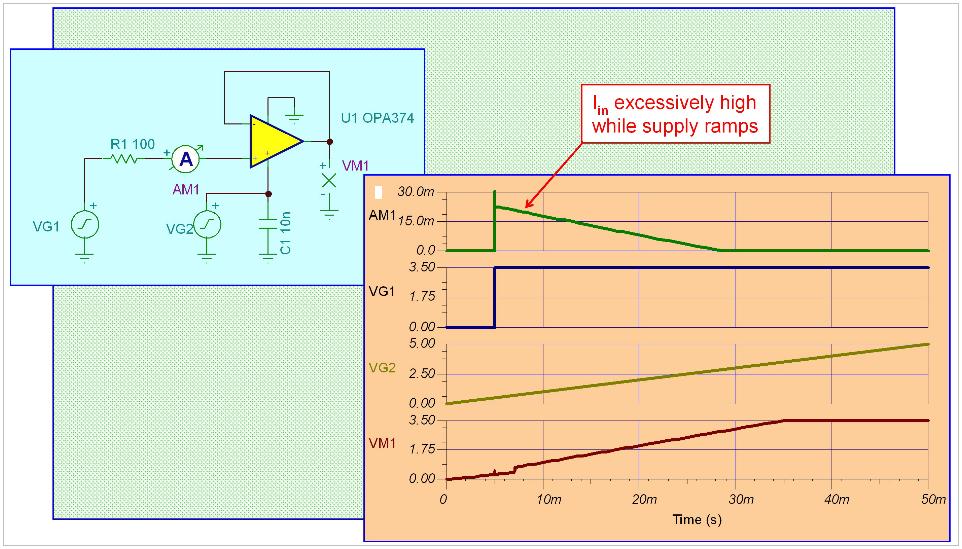

Běžná přepěťová událost může nastat tehdy, přivedeme – li k zesilovači napájecí napětí poté, co již máme na vstupu signál, viz obr. 2. Nebude – li pak vstupní proud obvodu

OPA374 (operační zesilovač, 6,5 MHz, rail-to-rail I/O, CMOS) omezen, může takový spouštěcí mechanismus poškodit vstupní ochranné ESD struktury zesilovače.

Obr. 2: Během náběhu napájecího napětí sledujte vstup neinvertujícího zesilovače!

(s využitím softwarového nástroje TINA)

Na obr. 2 vidíme nasimulované výsledky takového scénáře (TINA-TI, SPICE software od Texas Instruments). Napájení (VG2) zde během 50 ms poroste z 0 V na 5 V. Pět milisekund poté, co napájecí napětí začne stoupat, se na neinvertujícím vstupu zesilovače objeví vstupní signál (VG1) o velikosti 3,5 V. Krátce po uplynutí pěti milisekund bude vstupní napětí zesilovače větší než jeho kladná napájecí úroveň, takže dochází k aktivaci ESD diody neinvertujícího vstupu. Bude – li vstupní zdroj (VG1) nízkoimpedanční a je – li schopen dodávat proud, může ochrannou diodou teoreticky protéct nebezpečný proud. Vstupní struktury pak před zničením ochrání sériově zařazený vstupní rezistor.

Jev, při kterém dochází k elektrickému přetížení – EOS, může aktivovat ochranné ESD struktury uvnitř operačního zesilovače. To pak možná některé vývojáře vede k závěru, že ESD struktury rovněž budou odpovídajícím řešením v případě EOS. ESD stavy trvají velmi krátkou dobu, obvykle ne více než několik stovek nanosekund. EOS události naproti tomu mohou trvat mnohem déle. Dojde – li pak k aktivaci ESD prvku z titulu přetížení – EOS, obvody možná „povedou proudy, které povedou“ k nadměrnému ohřevu a případnému zničení prvku. Bude – li tedy Váš systém vystaven možnému přetěžování, učiňte vhodná opatření pro ochranu takového zapojení prostřednictvím jednoduché vnější ochranné struktury. Nepatrné vývojářské starosti, které snad budeme muset na počátku řešit, totiž vyloučí riziko závažnějších problémů během samotného provozu.

Download a odkazy:

-

Stáhněte si datasheet, případně i další technickou dokumentaci k obvodu OPA374: www.ti.com/opa374-ca.

-

Zjistěte více o ESD ochraně nebo si také stáhněte svou vlastní kopii příručky ESD and EMI Selection Guide od TI: www.ti.com/esd-ca.

-

Stáhněte si vlastní kopii simulačního programu TI pro analogovou techniku TINA-TI, založenou na SPICE: www.ti.com/tinati-ca.

Setkala jsem se již se zákazníky, kteří si stěžovali, že jim naše společnost odeslala špatný výrobek. Když jsem se pak zeptala na to, jakou poruchu součástka vykazuje, řekli mi: „Jen to nechce pracovat“. A tak zjišťuji, že si vývojáři mnohdy neuvědomují rizika, spojovaná s EOS (Electrical Overstress, v dalším textu budeme překládat jako elektrické přetížení), při kterých nechtěně vyrábí problémy tohoto druhu.

Setkala jsem se již se zákazníky, kteří si stěžovali, že jim naše společnost odeslala špatný výrobek. Když jsem se pak zeptala na to, jakou poruchu součástka vykazuje, řekli mi: „Jen to nechce pracovat“. A tak zjišťuji, že si vývojáři mnohdy neuvědomují rizika, spojovaná s EOS (Electrical Overstress, v dalším textu budeme překládat jako elektrické přetížení), při kterých nechtěně vyrábí problémy tohoto druhu.